Категории:

ДомЗдоровьеЗоологияИнформатикаИскусствоИскусствоКомпьютерыКулинарияМаркетингМатематикаМедицинаМенеджментОбразованиеПедагогикаПитомцыПрограммированиеПроизводствоПромышленностьПсихологияРазноеРелигияСоциологияСпортСтатистикаТранспортФизикаФилософияФинансыХимияХоббиЭкологияЭкономикаЭлектроника

Практическая реализация логических вентилей

Теперь мы перейдем к вопросу о практических средствах, используемых для представления логических переменных и логических функций. Совершенно очевидно, что выбор физического параметра, представляющего логические переменные, зависит от используемой технологии. В электронных схемах для этой цели может использоваться либо напряжение, либо сила электрического тока.

Для того чтобы установить соответствие между величиной напряжения и логическими значениями, или состояниями, в электронике используют концепцию порога (threshold). Напряжение, превышающее заданный порог, представляет одно значение, а напряжение, которое ниже этого порога, — совсем другое значение, а практике напряжение в любой точке электронной схемы подвержено небольшим случайным колебаниям, зависящим от множества причин. Из-за этого «шума» значения напряжения вблизи порога нельзя с уверенностью соотнести с конкретными логическими состояниями. Поэтому для электронных схем обычно устанавливают некоторый «запрещенный диапазон», как показано на рис. 3.14. напряжения ниже Vo,max представляют логическое значение 0, напряжения выше Vl,min — значение 1. Говоря о напряжении, соответствующем логическим значениям 0 и 1, мы будем использовать понятия «низкое» и «высокое».

Рис. 3.14. Представление логических значений посредством уровней напряжения

Мы начнем знакомство с электронными схемами, реализующими базовые логические функции, с описания простейших из них, которые состоят из резисторов и транзисторов, действующих в качестве переключателей. Для начала рассмотрим схемы, приведенные на рис. 3.15. Когда ключ S на рис. 3.15, а разомкнут, выходное напряжение Vout равно 0 («земля»). Когда же ключ S замкнут, выходное напряжение Vout равно напряжению источника Vsupply. Точно так же действует схема, когда роль ключа играет транзистор Т. Когда входное напряжение, подаваемое на затвор транзистора, равно 0 (то есть когда Vin = 0), ключ разомкнут и Vout = Vsupply. Когда

Рис. 3.15. Схемы инвертора: с использованием ключа (а); с транзистором в качестве ключа (б)

же значение Vin изменяется на Vsupply, ключ замыкается и выходное напряжение Vout становится близким к нулю. Таким образом, электронный ключ, схема которого показана на рис. 3.10, 6, может выполнять функции логического вентиля НЕ.

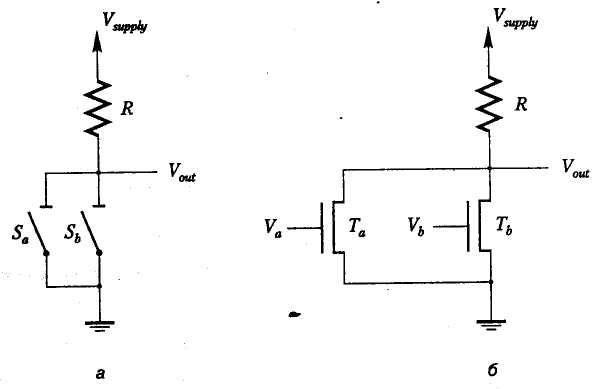

На рис. 3.16 показана электрическая цепь и эквивалентная ей электронная схема, реализующая вентиль ИЛИ-НЕ. На рис. 3.16, а выходное напряжение Vout будет

Рис. 3.16. Схемы, реализующие вентиль ИЛИ-НЕ: с использованием двух ключей (а); с транзистором в качестве ключа (б)

высоким только в том случае, если оба ключа, Sa и Sb будут разомкнуты. Аналогичным образом, выходное напряжение Vout на рис. 3.16, б будет высоким при условии, что входные напряжения Va и Vb низки. Поэтому данная схема эквивалентна вентилю ИЛИ-НЕ, где входные напряжения Va и Vbпредставляют две входные логические переменные, х1 и х2.

Вентиль ИЛИ-НЕ можно сконструировать из двух транзисторов, соединив их последовательно (рис. 3.17). Что касается логических функций И и ИЛИ, то они легко реализуются на основе вентилей И-НЕ и ИЛИ-НЕ — достаточно вслед за вентилем включить в цепь инвертор, показанный на рис. 3.15.

Рис. 3.17. Схемы, реализующие вентиль И-НЕ: с использованием двух ключей (а); с транзистором в качестве ключа (б)

Реализовать вентили И-НЕ и ИЛИ-НЕ несколько проще, чем И и ИЛИ. Поэтому неудивительно, что ими так часто пользуются при реализации логических функций.

Стараясь сделать примеры как можно понятнее, мы приводили много схем на основе вентилей И, ИЛИ и НЕ. Но на практике логические схемы могут содержать вентили всех пяти типов.

Приведенные выше рис. 3.14-3.17 отражают общую структуру электронных схем, создаваемых по технологии п-МОП (NMOS). В качестве ключей в электронных логических схемах используются металло-оксидные полупроводниковые транзисторы (МОП-транзисторы), которые бывают двух типов: n-канальные и р-канальные. N-канальные транзисторы называют транзисторами типа n-МОП. Когда на вход n-канального транзистора (то есть на его затвор) подается положительное напряжение источника питания, Vsupfly, ключ замыкается (рис. 3.18, а). Р-канальный транзистор действует наоборот: когда входное напряжение на его затворе VG равно Vsupfly, ключ разомкнут, а когда VG = 0, ключ замкнут (рис. 3.18, 6).

Замкнутый ключ, Разомкнутый ключ,

когда VG = Vsupfly когда VG = 0 В

а)

Замкнутый ключ, Разомкнутый ключ, когда

VG = Vsupfly когда VG = 0 В

б)

Рис. 3.18. Логические схемы транзисторов: n-МОП (а); р-МОП (б)

Обратите внимание на графическое обозначение транзистора р-МОП: кружок на входе показывает, что его действие противоположно действию транзистора n-МОП. Обратите также внимание, что у транзистора n-МОП символы s и d, обозначающие исток и сток, располагаются с противоположных сторон по сравнению с транзистором р-МОП. Исток n-канального транзистора соединяется с землей, а исток р-канального транзистора — с источником напряжения Vsupfly. (Указанные обозначения отражают направление движения тока в транзисторах.)

Электронные схемы, приведенные на рис. 3.14-3.17, имеют один недостаток: они требуют слишком большой мощности. В состоянии, когда ключи замкнуты и соединяют нагрузочный резистор R с «землей», электрический ток идет от источника напряжения Vsupfly к «земле». В противоположном состоянии, когда ключ разомкнут, соединения с «землей» нет, а значит, нет и тока. (В МОП- транзисторах ток через затвор не идет.) Таким образом, мощность, потребляемая электронными логическими схемами на МОП- транзисторах, зависит от состояния вентилей.

У данной проблемы имеется весьма эффективное решение: использовать в одной схеме транзисторы обоих типов, чтобы в устойчивом состоянии не потреблялась лишняя мощность. Эта идея была положена в основу технологии КМОП — построения схем на основе комплементарных (то есть дополняющих друг друга) металло-оксидных полупроводниковых транзисторов (Complementary Metal-Oxi-le Semiconductor, CMOS,).

Суть КМОП-технологии иллюстрирует схема инверторa, приведенная на рис. 3.19. Когда Vx=Vsupfly, что соответствует значению 1 входной переменой х1,

Рис. 3.19. КМОП-реализация вентиля НЕ: схема вентиля (а); таблица истинности и состояния транзисторов (б)

транзистор Т1 открыт, а транзистор Т2 закрыт. При этом выходное напряжение транзистора Т2 уменьшается от Vf до 0. Когда входное напряжение Vx становится равным 0, транзистор Т1 закрывается, а транзистор Т2 открывается. Выходное напряжение транзистора T1 увеличивается до Vsupfly . Таким образом, логические значения х и f дополняют друг друга и схема реализует вентиль НЕ.Суть этой схемы заключается в том, что транзисторы Т1 и Т2 действуют как логические дополнения: когда один из них закрыт, другой, наоборот, открыт. Поэтому точка выхода f всегда соединена либо с точкой Vsupfly, либо с «землей». При этом между «землей» и точкой Vsupfly никогда не бывает соединения, за исключением краткого переходного момента, когда изменяется состояние транзисторов Это означает, что в устойчивом состоянии данная схема потребляет минимум энергии, и утечка происходит только в моменты перехода из одного логического состояния в другое. Таким образом, количество энергии, потребляемой логической схемой, зависит от частоты изменения состояния ее элементов.

Теперь концепцию КМОП можно распространить на схемы с и входами, как показано на рис. 3.20.

Рис. 3.20. Структура КМОП-схемы

Транзисторы n-МОП используются для создания понижающей цепи, образующей соединение между точкой выхода f и «землей», когда реализуемая функция F(x1,…хn) равна 0. Повышающая цепь создается на основе транзисторов р-МОП — она образует соединение между точкой выхода f и точкой Vsupfly, когда F(x1,…хn) = 1. Повышающая и понижающая цепи функционально дополняют друг друга, для того чтобы в устойчивом состоянии напряжение в точке f равнялось либо Vsupfly, либо нулю («земля»).

Понижающая цепь, подобно схемам, приведенным на рис. 3.14-3.17, создается на основе транзисторов n-МОП. Как реализуются вентили И-НЕ и ИЛИ-НЕ, показано соответственно на рис. 3.21 и 3.22, а вентиль И, согласно рис. 3.23, реализуется путем инвертирования выходного сигнала вентиля И-НЕ.

Значительное уменьшение потребляемой схемой мощности — это не единственное достоинство технологии КМОП. Еще одним ее преимуществом является очень маленький размер МОП-транзисторов.

Рис. 3.21. МОП- реализация вентиля И-НЕ: схема вентиля (а); таблица истинности и состояния транзисторов (б)

Рис. 3.22. КМОП- реализация вентиля ИЛИ-НЕ: схема вентиля (а); таблица истинности и состояния транзисторов (б)

| Рис. 3.23. КМОП-реализация вентиля И | Рис. 3.24. Передаточная характеристика КМОП-инвертора |

А это важно по двум причинам. Во-первых, на основе этих транзисторов производятся микросхемы с невероятно высокой степенью интеграции элементов: на одном современном чипе умещаются миллионы транзисторов, благодаря чему один чип может содержать мощный микропроцессор или блок памяти большой емкости. Во-вторых, чем меньше транзистор, тем быстрее он переключается из одного состояния в другое. Быстродействие современных интегральных КМОП-микросхем измеряется в гигагерцах

Для современных КМОП-микросхем используются источники питания с напряжением от 1,5 до 15 В. Напряжение питания для наиболее распространенных микросхем равно 5 или 3,3 В. Чем меньше напряжение питания микросхемы, тем меньше потребляемая ею мощность (потребляемая мощность пропорциональна V2supfly) а значит, на микросхему можно поместить большее количество транзисторов, не вызывая ее перегрева. К сожалению, снижение напряжения ведет к понижению помехоустойчивости микросхемы, так что здесь требуется разумный компромисс.

На рис. 2.24 показано, как осуществляется переход между низким и высоким уровнями сигнала в КМОП-инверторе. Кривая, называемая передаточной характеристикой, отражает выходное напряжение как функцию входного напряжения. На данном рисунке видно, что когда входное напряжение проходит значение Vsupfly /2, выходное напряжение резко падает.

Это значение входного напряжения, обозначенное на рисунке как Vt, называется пороговым. Отмеченное на графике значение d, определяющее окрестность порогового напряжения, таково, что Vout » Vsupfly, если Vin < Vt - d, и V^ » 0, если Vin > Vt + d. Это значит, что для формирования правильного выходного сигнала входной сигнал не обязательно должен быть в точности равным номинальному значению 0 или Vsupfly . Допускается небольшая погрешность входного сигнала, называемая шумом, которая не вызывает нарушений в работе схемы.

Приемлемые границы шума называются запасом помехоустойчивости.

Для входного логического значения 1 запас помехоустойчивости составляет Vsupfly - (Vt + d), а для значения 0 он равен Vt - d. У микросхем КМОП запас помехоустойчивости очень высок.

Последнее изменение этой страницы: 2017-07-07

lectmania.ru. Все права принадлежат авторам данных материалов. В случае нарушения авторского права напишите нам сюда...