Категории:

ДомЗдоровьеЗоологияИнформатикаИскусствоИскусствоКомпьютерыКулинарияМаркетингМатематикаМедицинаМенеджментОбразованиеПедагогикаПитомцыПрограммированиеПроизводствоПромышленностьПсихологияРазноеРелигияСоциологияСпортСтатистикаТранспортФизикаФилософияФинансыХимияХоббиЭкологияЭкономикаЭлектроника

Мультиплексор и демультиплексоры

Мультиплексоры называют также селекторами данных. Действие механического коммутатора, показанного на рис. 3.28, а, идентично действию селектора данных электронного мультиплексора. Вращающийся коммутатор имеет восемь входов и один единственный выход. Вращением механической ручки данные с одного любого входа (0—7) могут быть переданы на выход и будут полностью идентичны входным.

На рис. 3.28, б приведена логическая схема мультиплексора-селектора данных на восемь входов. Обозначим их как I0— I7 и единственный выход как Y. Отметим также, что имеется один L-активный вход активизации  .

.

Рис 3.28. Механический коммутатор — аналог мультиплексора/селектора данных (а) и мультиплексор на восемь выходов (б)

Эти входы и выход представляют собой устройство, полностью аналогичное механическому коммутатору, и мы можем рассматривать вход активизации Е как общий прерыватель. Внизу на логической схеме мы обозначим выводы управления селекцией данных как S2, S1, S0. Двоичные данные, поданные на эти входы, определяют, какой из входов данных соединен с выходом.

Пример, приведенный на рис. 3.28,6, показывает, что цепь включена или активизирована L-сигналом на входе

На выводы селекции данных S2, S1, S0 подано 1012. Этот сигнал избирает вход 5, что обеспечивает передачу логической 1 с I5 на вход Y. Мультиплексор с восемью входами может быть использован для преобразования одного входного 8-разрядного слова в последовательный эшелон импульсов, переключая 3-разрядный счетчик на вводах селекции данных, что осуществляет последовательную селекцию входов (I0, I1, I2 и т. д.).

Мультиплексор-селектор данных используют также для решения сложных логических задач. Пример мультиплексорной схемы приведен на рис. 3.29.

У данной схемы два входных сигнала выбора — w и w2. Четыре возможные комбинации их значений используются для выбора одного из входов данных (х1, х2, х3 или х4), значение которого передается на выход z. Очевидно, такую же структуру будут иметь и большие мультиплексоры, в которых k входных сигналов выбора используются для соединения одного из 2k входов данных с выходом.

Типичной областью применения мультиплексоров является фильтрация данных, поступающих из множества разных источников. В частности, с помощью шестнадцати четырехвходовых мультиплексоров можно реализовать загрузку 16-разрядного регистра данных из одного из четырех источников.

Рис. 3.29. Четырехвходовый мультиплексор

Еще мультиплексоры используются в качестве базовых элементов для реалистических функций. Для примера рассмотрим функцию f определяемую таблицей истинности, приведенной на рис. 3.30. Чтобы упростить эту функцию, переменные

Рис. 3.30. Реализация логической функции на основе мультиплексора

х1 и х2 следует рассматривать отдельно, как показано на рисунке. Обратите внимание, что для каждой пары значений переменных x1 и х2 значение функции соответствует одному из четырех термов: 0, 1, х3 или  . Это означает, что функцию можно реализовать с помощью четырехвходовой мультиплексорной схемы, где переменные х1 и х2 используются для выбора одного из четырех сигналов. Далее, если на входы данных подаются значения 0,1, х3 или

. Это означает, что функцию можно реализовать с помощью четырехвходовой мультиплексорной схемы, где переменные х1 и х2 используются для выбора одного из четырех сигналов. Далее, если на входы данных подаются значения 0,1, х3 или  то согласно таблице истинности, на выход мультиплексора передается значение, соответствующее функции f. Это универсальный подход. Любую функцию трех переменных можно реализовать с помощью одного четырехвходового мультиплексора. Любую функцию четырех переменных подобным же образом можно реализовать с помощью одного восьмивходового мультиплексора и т.д.

то согласно таблице истинности, на выход мультиплексора передается значение, соответствующее функции f. Это универсальный подход. Любую функцию трех переменных можно реализовать с помощью одного четырехвходового мультиплексора. Любую функцию четырех переменных подобным же образом можно реализовать с помощью одного восьмивходового мультиплексора и т.д.

Демультиплексор, представленный на рис. 3.31, предназначен для выполнения действий, обратных действиям мультиплексора. Демультиплексор 1x8 обладает одним только входом данных D и восемью выходами (0—7). Схема имеет один L-вход активизации и три входа селекции данных В примере на рис. 3.31 имеется логическая 1 на входе D.

Цепь активизируется одним L-сигналом и входы селекции данных избирают выход 5 (1012). При этих условиях входные данные появляются на выходе 5.

Рис.3.31. Схема демультиплексора 1x8.

Соединением входов селекции данных с 3-разрядным счетчиком последовательно входящие данные могут быть распределены на восемь выходов один за другим. Мультиплексоры и демультиплексоры могут быть использованы совместно для преобразования непрерывной информации в форму последовательностей. Мультиплексор будет представлять собой эмиттер, демультиплексор — приемник, который передает данные в их начальной форме.

Дешифраторы

Значительная часть информации хранится и обрабатывается в компьютерах в закодированном виде. Например, если речь идет о машинной команде, то для ее хранения может использоваться n-битовое поле, вмещающее один из 2n различных кодов операций. Но прежде чем выполнить требуемую операцию, закодированная команда должна быть декодирована. Схема, которая способна принять входное значение, состоящее из и разрядов, и сгенерировать соответствующий выходной сигнал на одной из 2n выходных линий, называется дешифратором (или декодером).

Простейший пример дешифратора с двумя входами и четырьмя выходами показан на рис. 3.32. Одна из четырех выходных линий выбирается на основании

Рис. 3.32. Дешифратор с двумя входами и четырьмя выходами

значений на входах х1 и х2. На выбранный выход подается логическое значение 1, а на оставшиеся выходы — логическое значение 0. Существуют и другие полезные типы дешифраторов.

Так, при использовании двоично-десятичных данных обычно требуются декодирующие схемы, в которых четыре входные переменные, представляющие двоично-кодированное десятичное число, используются для выбора одного из 10 возможных выходов. В качестве еще одного специфического примера можно рассмотреть дешифратор, используемый для управления 7-сегментным индикатором.

Структура соответствующего 7-сегментного элемента показана на рис. 3.33.

Как видите, с его помощью можно отобразить любую десятичную цифру. Соответствующие функции для каждого из 7 сегментов индикатора приведены в таблице истинности на рис. 3.34. Они реализуются с помощью показанной на этом же рисунке электронной схемы, составленной из вентилей И-НЕ.

Модули интегральных микросхем

В предыдущих разделах были рассмотрены базовые принципы построения электронных схем для реализации логических функций. Для их практического воплощения используются серийно производимые интегральные схемы (ИС). Когда в 1960-х годах появились первые интегральные схемы, логические вентили стали выпускать в виде стандартизированных чипов. Такой чип монтировался в полностью закрытый защитный корпус со множеством металлических контактов для соединения с внешним устройством. Стандартные модули ИС имели разное количество контактов. На рис. 3.35 показан простейший модуль с четырьмя вентилями И-НЕ. логическая структура схемы с четырьмя 2-входовыми вентилями И-НЕ (б)

Эти четыре вентиля имеют общие контакты для соединения с «землей» и источником питания. Подобные ИС, содержащие всего несколько логических вентилей, называются схемами с малой степенью интеграции или малыми интегральными схемами (МИС).

Рис. 3.33. Дешифратор, преобразующий двоично-десятичное число для отображения на 7-сегментном индикаторе

Рис. 3.34. Таблица истинности

Рис. 3.35. Модуль 14-контактной интегральной схемы: внешний вид (а);

Для столь простых функций, которые выполняют малые интегральные схемы, они занимают слишком много физического пространства. Более того, их производительность довольно низка из-за электрических характеристик контактов модуля ИС. Чтобы сгенерировать сигналы достаточной мощности, необходимые для управления устройствами и схемами, подсоединенными к внешним контактам, приходится использовать большие транзисторы. В результате задержка на распространение сигнала и потребляемая схемой мощность заметно увеличиваются.

Время задержки на распространение сигнала для КМОП-вентиля И-НЕ, который входит в состав модуля интегральных может достичь 5 нс. В случае таких же вентилей, используемых в больших интегральных схемах КМОП, задержка обычно составляет не более 0,2 нс, что зависит от технологии производства.

В настоящее время производятся гораздо более крупные ИС, реализующие образные логические элементы. Чип интегральной схемы может содержать полезный функциональный блок, такой как сумматор, умножитель, регистр, шифратор или дешифратор, либо просто набор вентилей и программируемых переключателей внутренних соединений, с помощью которых конструктор может реализовать множество разных функций.

Триггеры и защелки

Логические цепи могут быть разделены на две большие группы. Первая —цепи комбинационной логики, составленные из логических элементов, вторая — последовательные логические цепи, состоящие из элементов, называемых триггерами. Триггеры объединяют в системы с целью образования последовательных логических цепей, предназначенных для размещения данных, обеспечения нужной временной задержки, вычислений и формирования требуемых последовательностей сигналов. Триггеры обладают важной способностью запоминания. Триггер запомнит свои входные сигналы даже тогда, когда эти сигналы будут сняты.

Термином триггер (flip-flop) называют запоминающий элемент, выходное состояние которого меняется на фронте управляющего тактового сигнала (то есть в момент его перехода из одного состояния в другое). Логический элемент, напротив, не сможет запомнить свое состояние на выходе, если будут сняты входные сигналы.

На рис. 3.36 приведена очень широко используемая схема D-триггера (называемого также триггером данных). Отметим здесь два входа, обозначенных D (для данных) и СК (для сигналов синхронизации или тактовый вход).

Рис.3.36. D–триггер

Триггер имеет обычно два взаимно инверсных выхода, обозначенных Q и  (HE-Q). Выход Q используется более часто и называется нормальным. Выход Q называется дополнительным или инверсным выходом триггера. Графическое обозначение «>» на входе СК логической схемы D-триггера указывает, что этот триггер передает данные со входа на выход при положительном фронте ( ) тактовых импульсов. Операционные состояния D-триггера приведены в левой колонке таблицы истинности или таблицы переходов триггера (табл. 3.9), где 0 - LOW; 1 - HIGH; *— не имеет значения; — переход от LOW к HIGH тактового импульса.

(HE-Q). Выход Q используется более часто и называется нормальным. Выход Q называется дополнительным или инверсным выходом триггера. Графическое обозначение «>» на входе СК логической схемы D-триггера указывает, что этот триггер передает данные со входа на выход при положительном фронте ( ) тактовых импульсов. Операционные состояния D-триггера приведены в левой колонке таблицы истинности или таблицы переходов триггера (табл. 3.9), где 0 - LOW; 1 - HIGH; *— не имеет значения; — переход от LOW к HIGH тактового импульса.

Таблица 3.9

Таблица истинности статистических состояний D - триггера

| Операционные состояние | Входы | Выходы |

| D СК | Q

| |

| Активизация Сброс Ожидание | 1 0 * Отсутствие | 1 0 0 1 Предыдущее состояние |

Установить (или активизировать) триггер означает, что на нормальном выходе Q устанавливается 1. Первая строка таблицы истинности показывает, что подачей 1 на вход D-триггера при положительном тактовом импульсе СК на выходе Q устанавливается 1. Вторая строка соответствует сбросу (установке в нуль) триггера. Сбросить триггер означает вернуть выход Q в состояние 0. Установить состояние ожидания - это значит сохранить на выходе данные предыдущего состояния. Когда триггер находится в состоянии ожидания, изменения логических состояний данных на входе не влияют на состояние выходов. Состояние ожидания характеризует способность триггера запоминать сигналы. Отметим, что операции установки и сброса рассматриваются по отношению к выходу Q.

Большинству устройств, в которых задействована цифровая логика, требуются элементы для хранения информации. Например, схема управления кодовым замком должна запоминать последовательность открывающего его набора цифр. Еще один важный пример — электронная память для хранения данных, необходимая цифровым компьютерам. Базовый электронный элемент, используемый для хранения информации, называется защелкой (latch). Рассмотрим логическую схему, приведенную на рис. 3.37, на которой изображена 4-разрядная прозрачная защелка.

Рис. 3.37. Логическая схема прозрачной 4-разрядной защелки

Каждый триггер-защелка, входящий в это устройство, является устройством либо памяти, либо размещения данных. Для лучшего понимания состава регистра-защелки необходимо рассматривать его состоящим из четырех D-триггеров, тактовые входы которых объединены одним входом разрешения (или активизации). Согласно соответствующей таблице истинности (табл. 3.10) при поступлении 1 на вход Е (Н-сигнал) данные со входов D0—D3 будут переданы на выходы Q0— Q3 соответственно. Четырехразрядное слово поступает на входы в параллельной (но не в последовательной) форме и передается на выходы в той же форме.

Таблица 3.10

| Функциональное состояние | Входы | Выход |

| D Е | Q | |

| Признание данных | 0 1 1 1 | |

| Захват данных | * 0 | Предыдущее состояние |

Тактирование фронтом сигнала

Триггер называется тактируемым фронтом сигнала, если поданные на его вход данные передаются на выход только в момент изменения тактового сигнала. Все остальное время вход и выход изолированы друг от друга. Термины тактируемый положительным (передним) фронтом сигнала и тактируемый отрицательным (задним) фронтом сигнала относятся к триггерам, в которых передача данных происходит в ответ на изменение тактового сигнала соответственно с 0 на 1 и с 1 на 0. Для корректного функционирования триггера, тактируемого фронтом сигнала, необходимо, чтобы фронт тактового сигнала был четко определен и имел очень малое время перехода. На рис. 3.38 изображен двухступенчатый триггер тактируемый отрицательным фронтом сигнала.

Другой способ реализации двухступенчатого триггера, тактируемого отрицательным фронтом сигнала, показан на рис. 3.39, а. Посмотрим, как действует этот триггер. Если Clk=1, на выходы вентилей 2 и 3 подается сигнал 0. Поэтому состояние на выходах триггера Q и  сохраняется неизменным. Нетрудно убедиться, что пока Clk=1, точки РЗ и Р4 немедленно отражают изменения на входе D.

сохраняется неизменным. Нетрудно убедиться, что пока Clk=1, точки РЗ и Р4 немедленно отражают изменения на входе D.

Рис. 3.38. Двухступенчатый D-триггер: схема (а); временная диаграмма (б); графическое обозначение (в)

Рис. 3.39. D-триггер, тактируемый отрицательным фронтом сигнала: схема (а); пример временной диаграммы (б)

Сигнал в точке РЗ остается равным сигналу  , а сигнал осе Р4 — равным D. Когда на вход Сlк поступает сигнал 0, эти значения передаются в точки Р1 и Р2 с помощью вентилей 2 и 3 соответственно. Таким образом выходная защелка, состоящая из вентилей 5 и 6, переходит в новое состояние, которое она теперь должна хранить.

, а сигнал осе Р4 — равным D. Когда на вход Сlк поступает сигнал 0, эти значения передаются в точки Р1 и Р2 с помощью вентилей 2 и 3 соответственно. Таким образом выходная защелка, состоящая из вентилей 5 и 6, переходит в новое состояние, которое она теперь должна хранить.

Мы сможем убедиться в том, что дальнейшие изменения значений на входе D при Clk=0 не влияют на сигналы в точках Р1 и Р2, рассмотрев два случая. Для начала предположим, что на отрицательном фронте сигнала Clk вход D равен 0.

Единичный сигнал в точке Р2 сохраняет значение 1 на соответствующих входах шлей 2 и 4, в результате чего, независимо от дальнейших изменений сигнала ходе D, в точках Р1 и Р2 сохраняются соответственно значения 0 и 1. Теперь предположим, что на отрицательном фронте сигнала Clk вход D=1. Сигнал 1 в точке Р1

означает, что дальнейшие изменения, на входе D не могут воздействовать на выход вентиля 1, где сохраняется сигнал 0.

Когда в начале следующего тактового импульса значение Clk меняется на 1, в точках Р1 и Р2 снова появляется сигнал 0, изолирующий выход от остальной части схемы. После этого точки РЗ и Р4 отражают, как было сказано выше, изменения в точке D.

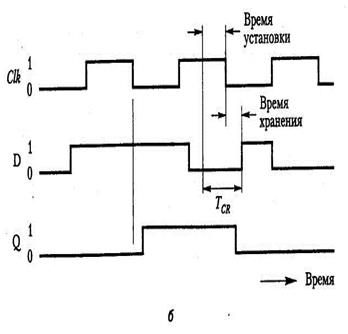

Как работает этот тип D-триггера, показано на рис. 3.39, б. Значение на выходе, которое появится после того, как сигнал на входе Clk изменится с 1 на 0, будет равно значению на входе D триггера непосредственно перед этим переходом. Однако непосредственно перед отрицательным фронтом сигнала Clk и сразу после такового существует критический период времени TCR, в течение которого значение D не должно изменяться. Этот промежуток времени, как показано на рисунке, разделяется на две части: время установки и время хранения. На временной диаграмме видно, что выходное значение Q изменяется с небольшой задержкой те отрицательного фронта тактового сигнала. Причиной этого является задержка на распространение сигнала в вентилях ИЛИ-НЕ.

JK-триггеры

Такая передача называется параллельным вводом/выводом. Защелка размещения (или хранения) данных является одной из разновидностей среди разных типов триггеров.

JK-триггеры - это еще один тип триггеров, который, правда, используется менее часто, нежели описанные выше. JK-триггер обладает чертами триггеров SR и Т. Его схема, таблица истинности и обозначение приведены на рис. 3.40. Первые три строки в таблице истинности JK-триггера определяют его поведение, аналогичное поведению вентильной SR-защелки при Clk = 1 (рис. 3.40, б), так что входы J и К соответствуют входам S и R. При входном сигнале J = К = 1 следующее состояние триггера определяется как дополнение его текущего состояния. Это означает, что когда J = К = 1, триггер действует как переключатель, изменяя свое текущее состояние на противоположное. JК-триггер можно реализовать на основе D-триггера и нескольких вентиле соединенных таким образом, что D = J  +

+  Q.

Q.

Соответствующая схема показана на рис. 3.40, а. Триггеры JK могут применяться для разных целей. В частности, их подобно триггерам можно использовать для хранения данных. входа данных J и K и один тактовый вход СК. JK-триггер имеет два традиционных выхода - Q (нормальный) и  (инверсный).

(инверсный).

Рис. 3.40. JK-триггер: схема (а); таблица истинности (б); графическое обозначение (в)

На их основе также можно создавать счетчики, поскольку при соединении терминалов J и К они ведут себя как Т-триггеры.

JK - триггер является наиболее употребительным триггером в последовательных логических цепях.

На рис. 3.41 приведена логическая схема типового JK-триггера. Она имеет два

Рис. 3.41. JK-триггер

JK -триггер имеет четыре операционных режима (см. табл. 3.11). Режим триггера означает, что при каждом тактовом импульсе выходы перейдут в логическое состояние, обратное тому, которое он имел до этого импульса. В этом случае выход Q JK -триггера будет проходить состояния HIGH-LOW-HIGH-LOW и т. д. по мере следования тактовых импульсов.

Таблица 3.11

Таблица истинности состояний JK - триггера

| Функциональные режимы | Входы | Выходы |

| J К СК | Q

| |

| Триггер Активизация Сброс Ожидание | 1 1 ¯ 1 0 ¯ 0 1 ¯ 0 0 ¯ | Противоположно предыдущему 1 0 0 1 Нет изменений |

Таблица истинности (см. табл. 3.11) показывает, что JK -триггер будет переключаться, когда два входа J и К находятся в Н-состоянии. В этот момент тактовый импульс поступает на вход СК. Эффективные переключения происходят, когда тактовый импульс переходит из Н- в L - cocтояние, как показывает стрелка в таблице истинности.

Находится JK -триггер в режиме инициализации (активизации), когда два входа данных J =1 и К = 0. Мы видим, что согласно второй строке таблицы истинности переход от Н- к L-состоянию тактовых импульсов переводит выход Q в состояние 1. Режим сброса или дезактивации (установка Q в 0) представлен третьей строкой таблицы истинности. Далее в таблице истинности приведен режим ожидания (отсутствие каких-либо действий JK -триггера. Когда оба входа данных (J и К) являются LOW, тактовый импульс на входе СК не оказывает никакого влияния на выход.

Запуск триггеров является важным этапом их функционирования. По способу запуска триггеры могут быть классифицированы на устройства, активизированные фронтом импульсов или уровнем импульсов. Логические схемы, приведенные на рис. 3.39, показывают, что соответствующие триггеры запускаются фронтом импульсов [наличие на схеме знака «>» (больше чем) на входе СК тактовых импульсов]. D -триггер запускается при переходе тактовых импульсов от L- к Н-уровню. Это показано в таблице истинности и на логической схеме (нет кружка инверсии на входе СК, что указывает на необходимость 1 для активизации тактовых импульсов).

D-триггер называется также триггером, запускаемым положительным фронтом тактовых импульсов, так как запуск осуществляется положительной частью тактовых импульсов.

Запускается JK-триггер отрицательным фронтом тактовых импульсов, что показано в таблице истинности (табл. 3.11) и на логической схеме (рис. 3.41). Кружок инверсии на входе СК JK -триггера указывает на необходимость L-сигнала для активизации входа тактовых импульсов. В случае, когда этот триггер запускается фронтом импульсов, для его запуска нужен переход тактовых импульсов от Н- к L-уровню.

Прозрачная 4-разрядная защелка, приведенная на рис. 3.37, является устройством, запускаемым уровнем тактовых импульсов. Это означает, что когда на вход активизации Е (подобный входам СК триггеров) поступает Н-сигнал, все двоичные данные на входах (D3—D0) тотчас появляются на выходах (Q3—Q0). Такая защелка называется прозрачной.

D- и T-триггеры

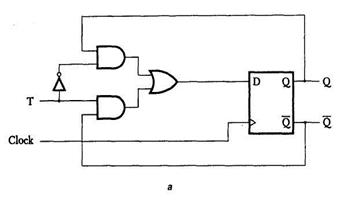

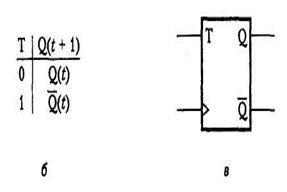

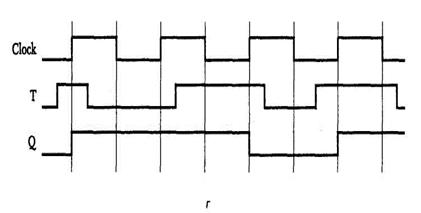

Наиболее часто используемым типом триггеров являются D-триггеры, поскольку могут использоваться для временного хранения данных. Однако во многих случаях требуются триггеры других типов. Например, схемы счетчиков, эффективнее реализуются на основе триггеров типа Т (рис. 3.42).

Рис. 3.42. Т-триггеры

Состояние Т-триггера изменяется на каждом такте, если на его вход Т подается значение 1. Говорят, что такой триггер «переключает» свое состояние, схема Т-триггера, а также его таблица истинности, графическое обозначение, мер временной диаграммы представлены на рис. 3.43, а. Как следует из рисунка, в основе Т-триггера лежит D-триггер. Обратите внимание, что D-триггер тактируется положительным фронтом сигнала.

Рис. 3.43. Т-триггер: схема (a), таблица истинности (б); графическое обозначение (в); временная диаграмма (г)

Последнее изменение этой страницы: 2017-07-07

lectmania.ru. Все права принадлежат авторам данных материалов. В случае нарушения авторского права напишите нам сюда...