Категории:

ДомЗдоровьеЗоологияИнформатикаИскусствоИскусствоКомпьютерыКулинарияМаркетингМатематикаМедицинаМенеджментОбразованиеПедагогикаПитомцыПрограммированиеПроизводствоПромышленностьПсихологияРазноеРелигияСоциологияСпортСтатистикаТранспортФизикаФилософияФинансыХимияХоббиЭкологияЭкономикаЭлектроника

Динамическая и статическая память

Память, применяемая для временного хранения инструкций и данных в компьютерной системе, получила название RAM (Random Access Memory — память с произвольной выборкой), потому что обращение происходит в любой момент времени к произвольно выбранной ячейке.

Память этого класса подразделяется на два типа - с динамической (Dynamic RAM, DRAM) и статической (Static RAM, SRAM) выборкой. В первом случае (рис. 5.3) значение бита информации в ячейке определяется наличием или отсутствием

Рис. 5.3. Принципиальная схема ячейки динамической памяти

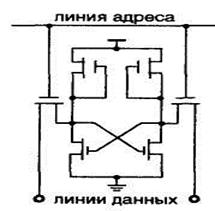

заряда на миниатюрном конденсаторе (управляемом 1-2 транзисторами). В статической памяти применены специальные элементы (рис. 5.4) - триггеры (имеющие

Рис. 5.4. Принципиальная схема ячейки статической памяти на

шести транзисторах

два устойчивых состояния), реализованные на 4-6 транзисторах. Естественно, что из-за необходимости ожидания накопления (стекания) заряда на конденсаторе быстродействие DRAM ниже. Однако благодаря большему числу транзисторов на ячейку память SRAM существенно дороже. Обычно модули DRAM применяют в оперативной и видеопамяти, а модули SRAM — в качестве быстрых буферных (Cash) элементов в процессорах, на материнских платах, в жестких дисках, приводах CD-ROM и прочих устройствах.

Память типа DRAM

Динамическая оперативная память (рис. 5.3) (Dynamic RAM — DRAM) используется в большинстве систем оперативной памяти современных персональных компьютеров. Основное преимущество памяти этого типа состоит в том, что ее ячейки упакованы очень плотно, т. е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости.

Ячейки памяти в микросхеме DRAM — это крошечные конденсаторы, которые удерживают заряды. Именно так (наличием или отсутствием зарядов) и кодируются биты.

Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут "стекать" и данные будут потеряны. Регенерация происходит, когда контроллер памяти системы берет крошечный перерыв и обращается ко всем строкам данных в микросхемах памяти. Большинство систем имеют контроллер памяти (обычно встраиваемый в набор микросхем системной платы), который настроен на соответствующую промышленным стандартам частоту регенерации, равную 15 мкс. Ко всем строкам данных обращение осуществляется по прохождении 128 специальных циклов регенерации. Это означает, что каждые 1,92 мс (128x15 мкс) прочитываются все строки в памяти для обеспечения регенерации данных.

Регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10% (или больше) процессорного времени, но в современных системах, работающих на частотах, равных сотням мегагерц, расходы на регенерацию составляют 1% (или меньше) процессорного времени. Некоторые системы позволяют изменить параметры регенерации с помощью программы установки параметров CMOS, но увеличение времени между циклами регенерации может привести к тому, что в некоторых ячейках памяти заряд "стечет", а это вызовет сбои памяти. В большинстве случаев надежнее придерживаться рекомендуемой или заданной по умолчанию частоты регенерации. Поскольку затраты на регенерацию в современных компьютерах составляют менее 1%, изменение частоты регенерации оказывает незначительное влияние на характеристики компьютера. Одним из наиболее приемлемых вариантов является настроек, заданных с помощью Setup BIOS. Большинство современных систем не позволяют изменять заданную синхронизацию памяти, постоянно используя автоматически установленные параметры. При автоматической установке системная плата считывает параметры синхронизации из системы обнаружения последовательности в ПЗУ (serial presence detect — SPD) и устанавливает частоту периодической подачи импульсов в соответствии с полученными данными.

В устройствах DRAM для хранения одного бита используется только один транзистор и пара конденсаторов, поэтому они более вместительны, чем микросхемы других типов памяти. В настоящее время имеются микросхемы динамической оперативной памяти емкостью 512 Мбайт и больше. Это означает, что подобные микросхемы содержат более 256 млн. транзисторов! А ведь Pentium 4 имеет только 42 млн. транзисторов. Откуда такая разница? Дело в том, что в микросхеме памяти все транзисторы и конденсаторы размещаются последовательно, обычно в узлах квадратной решетки, в виде очень простых, периодически повторяющихся структуру отличие от процессора, представляющего собой более сложную схему различных структур, не имеющую четкой организации.

Транзистор для каждого одноразрядного регистра DRAM используется для чтения состояния смежного конденсатора. Если конденсатор заряжен, в ячейке записана 1; если заряда нет — записан 0. Заряды в крошечных конденсаторах все время стекают, вот почему память должна постоянно регенерироваться. Даже мгновенное прерывание подачи питания или какой-нибудь сбой в циклах регенерации приведет к потере заряда в ячейке DRAM, а следовательно, и к потере данных. В работающей системе подобное приводит к появлению «синего» экрана, глобальным отказам системы защиты, повреждению файла или к полному отказу системы.

Динамическая оперативная память используется в персональных компьютерах; поскольку она недорогая, микросхемы могут быть плотно упакованы, а это означает, что запоминающее устройство большой емкости может занимать небольшое пространство.

К сожалению, память этого типа не отличается высоким быстродействием, обычно она намного "медленнее" процессора. Поэтому существует множество различных этапов организации DRAM, позволяющих улучшить эту характеристику.

Статическая память

Ячейкой в статической памяти является триггер (рис. 5.4) - логический элемент с двумя устойчивыми состояниями, в любом из которых он сохраняется до тех пор, пока подается питание. Время срабатывания триггера составляет в современных микросхемах единицы наносекунд. Однако плотность компоновки ячеек SRAM существенно ниже, чем в микросхемах DRAM, а стоимость производства выше, поэтому статическая память применяется лишь в наиболее ответственных компонентах.

В современных системах обычно используется конвейерный режим с пакетным способом передачи данных (Pipelined Burst Cache), организованный на микросхемах статической памяти с синхронным доступом.

Необходимым элементом подсистемы памяти является так называемая кэш-память (от английского Cache — запас). Она служит в качестве буферной «емкости» при обмене данными между процессором и оперативной (системной) памятью. Так как кэш организован на микросхемах типа SRAM (Static Random Access Memory — статическая память с произвольным доступом), которые работают примерно на порядок быстрее микросхем памяти типа DRAM, процессор обрабатывает данные из кэш-памяти сразу.

SDRAM

Это тип динамической оперативной памяти DRAM, работа которой синхронизируется с шиной памяти. SDRAM передает информацию в высокоскоростных пакетах, использующих высокоскоростной синхронизированный интерфейс. SDRAM позволяет избежать использования большинства циклов ожидания, необходимых при работе асинхронной DRAM, поскольку сигналы, по которым работает память такого типа, синхронизированы с тактовым генератором системной платы.

Как и для оперативной памяти EDO, для памяти этого типа требуется поддержка набором микросхем системной логики. Начиная с наборов 430VX и 430ТХ, выпяленных в 1997 году, все наборы микросхем системной логики компании Intel полностью поддерживают SDRAM. Этот тип памяти стал самым популяным в новых системах, выпущенных в 2000 и 2001 годах.

Эффективность SDRAM значительно выше по сравнению с оперативной памятью FPM или EDO. Поскольку SDRAM — это тип динамической оперативной памяти, ее начальное время ожидания такое же, как у памяти FPM или EDO, но общее время цикла намного короче. Схема синхронизации пакетного доступа SDRAM выглядит так 5-1-1-1 т. е. четыре операции чтения завершаются всего лишь за восемь циклов системной шины (сравните с 11 циклами для EDO и 14 для FPM).

Кроме этого, память SDRAM может работать на частоте 133 МГц (7,5 нс) и выше, что стало новым стандартом для системного быстродействия начиная с 1998 года. Фактически все новые персональные компьютеры, проданные с 1998 по 2000 год, имеют память типа SDRAM.

Память SDRAM поставляется в виде модулей DIMM и, как правило, ее быстродействие оценивается в мегагерцах, а не наносекундах.

Кэш-память — SRAM

Существует тип памяти, совершенно отличный от других, — статическая оперативная память (Static RAM — SRAM). Она названа так потому, что, в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требуется периодической регенерации. Но это не единственное ее преимущество. SRAM имеет более высокое быстродействие, чем динамическая оперативная память, и может работать на той же частоте, что и современные процессоры.

Время доступа SRAM не более 2 нс; это означает, что такая память может работать синхронно с процессорами на частоте 500 МГц или выше. Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких-либо конденсаторов означает, что нет необходимости в регенерации. (Ведь если нет никаких конденсаторов, то и заряды не теряются.) Пока подается питание, SRAM будет помнить то, что сохранено и используются память по таблице 5.2

Таблица 5.2

| Тип | Быстродействие | Плотность | Стоимость |

| Динамическая оперативная память – DRAM Статистическая оперативная память - SRAM | Низкое Высокое | Высокая Низкая | Низкая Высокая |

По сравнению с динамической оперативной памятью быстродействие SRAM намного выше, но плотность ее гораздо ниже, а цена довольно высока. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое количество транзисторов и кластеризованное их размещение не только увеличивает габариты микросхем SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM. Например, емкость модуля DRAM может равняться 64 Мбайт или больше, в то время как емкость модуля SRAM приблизительно того же размера составляет только 2 Мбайт, причем их стоимость будет одинаковой. Таким образом, габариты SRAM в среднем в 30 раз превышают размер динамической оперативной памяти, тоже самое можно сказать и о стоимости. Все это не позволяет использовать память типа SRAM в качестве оперативной памяти в персональных компьютерах.

Несмотря на это, разработчики все-таки применяют память типа SRAM для повышения эффективности РС. Но во избежании значительного увеличения стоимости устанавливается только небольшой объем высокоскоростной памяти SRAM, которая используется в качестве кэш-памяти. Кэш-память работает на тактовых частотах, близких или даже равным тактовым частотам процессора, причем обычно именно эта память непосредственно используется процессором при чтении и записи. Во время операций чтения данные в высокоскоростную кэш-память предварительно записываются из оперативной памяти с низким быстродействием, т. е. из DRAM. Еще недавно время доступа динамической оперативной памяти было не менее 60 нс (что соответствует тактовой частоте 16 МГц). Для преобразования времени доступа из наносекунд в мегагерцы используется следующая формула:

1/наносекунды х 1000 = МГц.

Обратное вычисление осуществляется с помощью такой формулы: 1/МГц х 1000 = наносекунды.

Когда процессор персонального компьютера работал на тактовой частоте 16 МГц и ниже, DRAM могла быть синхронизирована с системной платой и процессором, поэтому кэш был не нужен. Однако как только тактовая частота процессора поднялась выше 16 МГц, синхронизировать DRAM с процессором стало невозможно, и именно тогда разработчики начали использовать SRAM в персональных компьютерах. Это произошло в 1986-87 годах, когда появились PC с процессором 386, работающим на частотах 16 и 20 МГц. Именно в этих персональных компьютерах впервые нашла применение так называемая кэш-память, т. е. высокоскоростной буфер, построенный на микросхемах SRAM, который непосредственно обменивается данными с процессором. Поскольку быстродействие кэша может быть сравнимо с быстродействием процессора, контроллер кэша может предугадывать потребности процессора в данных и предварительно загружать необходимые данные в высокоскоростную кэш-память. Тогда при выдаче процессором адреса памяти данные могут быть переданы из высокоскоростного кэша, а не из оперативной памяти, быстродействие которой намного ниже.

Эффективность кэш-памяти выражается коэффициентом совпадения, или коэффициентом успеха. Коэффициент совпадения равен отношению количества удачных обращений в кэш к общему количеству обращений. Попадание — это событие, состоящее в том, что необходимые процессору данные предварительно считываются в кэш из оперативной памяти; иначе говоря, в случае попадания процессор может считывать данные из кэш-памяти. Неудачным обращением в кэш считается такое, при котором контроллер кэша не предусмотрел потребности в данных, находящихся по указанному абсолютному адресу. В таком случае необходимые данные не были предварительно считаны в кэш-память, поэтому процессор должен отыскать их в более медленной оперативной памяти, а не в быстродействующем кэше. Когда процессор считывает данные из оперативной памяти, ему приходиться какое-то время «ждать», поскольку тактовая частота оперативной памяти значительно ниже, чем процессора. Если процессор со встроенной в кристалл кэш-памятью работает на частоте 2000 МГц (2 ГГц), то продолжительность цикла процессора и интегральной кэш-памяти в этом случае достигнет 0,5 нс, в то время как продолжительность цикла оперативной памяти будет в шесть раз больше, т. е. примерно 3 или 6 нс для памяти с удвоенной скоростью передачи данных (Double Data Rate — DDR). Таким образом, тактовая частота памяти будет всего лишь 333 МГц. Следовательно, в этом случае, когда процессор с тактовой частотой 2 ГГц считывает данные из оперативной памяти, его рабочая частота уменьшается в шесть раз, что и составляет 333 МГц. Замедление обусловлено периодом ожидания (wail stale). Если процессор находится в состоянии ожидания, то на протяжении всего цикла (такта) никакие операции не выполняются; процессор, по существу, ждет, пока необходимые данные поступят из более медленной оперативной памяти. Поэтому именно кэш-память позволяет сократить количество "простоев" и повысить быстродействие компьютера в целом.

Чтобы минимизировать время ожидания при считывании процессором данных из медленной оперативной памяти, в современных персональных компьютерах обычно предусмотрены два типа кэш-памяти: кэш-память первого уровня (L1) и кэш-память второго уровня (L2). Кэш-память первого уровня также называется встроенным или внутренним кэшем, он непосредственно встроен в процессор и фактически является частью микросхемы процессора. Во всех процессорах 486 и выше кэш-память первого уровня интегрирована в микросхему процессора. Кэш-память второго уровня называется вторичным или внешним кэшем; он устанавливается вне микросхемы процессора. Первоначально она устанавливалась на системной плате. (Так было во всех компьютерах на основе процессоров 386, 486 и Pentium.) Если кэш-память второго уровня установлена на системной плате, то она работает на ее частоте. В этом случае кэш-память второго уровня обычно находится рядом с разъемом процессора.

Для повышения эффективности в более поздних компьютерах на основе процессоров Pentium Pro, Pentium II/Ш и Athlon кэш-память второго уровня является частью процессора. Конечно же, он внешний по отношению к кристаллу центрального процессора, просто эта отдельная микросхема устанавливается внутри корпуса (картриджа) процессора. Поэтому на системных платах для процессоров Pentium Pro или Pentium П нет никакого кэша.

В последних моделях процессоров Pentium Ш и Athlon кэш- память второго уровня является частью микросхемы процессора (подобно кэш-памяти первого уровня) и работает на более высоких частотах (на частоте процессора, половинной или трети). В процессорах Itanium для увеличения производительности используется три уровня кэш-памяти.

Первоначально кэш-память проектировалась как асинхронная, т. е. не была синхронизирована с шиной процессора и могла работать на другой тактовой частоте. При внедрении набора микросхем системной логики Intel 430FX в начале 1995 года был разработан новый тип синхронной кэш-памяти. Она работает синхронно с шиной процессора, что повышает ее быстродействие и эффективность. В то же время был добавлен режим pipeline burst mode (конвейерный монопольный режим). Он позволил сократить время ожидания за счет уменьшения количества состояний ожидания после первой передачи данных. Использование одного из этих режимов подразумевает наличие другого. Оба режима позволяют повысить производительность компьютера на 20%.

Контроллер кэш-памяти для современной системы содержится в микросхеме North Bridge набора микросхем системной логики в PC на основе Pentium и более простых или на плате процессора, как в случае с Pentium Pro, Pentium II/III и более новыми системами. Возможности контроллера кэш-памяти предопределяют эффективность и возможности кэш-памяти.

Часто этот предел может быть очень низок, как в случае набора микросхем системной логики 430ТХ для компьютеров на основе Pentium. Этот набор микросхем может кэшировать данные только первых 64 Мбайт оперативной памяти системы. Если установлен больший объем памяти, работа компьютера значительно замедляется, потому что все данные вне первых 64 Мбайт никогда не попадут в кэш и при обращении к ним будут всегда необходимы все состояния ожидания, определяемые более медленной динамической оперативной памятью. Снижение эффективности зависит от программного обеспечения и от адресов, по которым хранятся данные в памяти. Например, 32-разрядные операционные системы Windows загружаются сверху вниз, так что если установлена оперативная память емкостью 96 Мбайт, то и операционная система, и прикладные программы будут загружаться в верхние 32 Мбайт, которые не кэшируются. Это значительно замедлит работу компьютера в целом. В данном случае можно удалить дополнительную память, чтобы уменьшить емкость до 64 Мбайт. Другими словами, неблагоразумно устанавливать большую емкость памяти, чем позволяет кэшировать набор микросхем системной логики.

Процессор Pentium П и наборы микросхем системной логики более поздних версий не позволяют управлять кэш-памятью второго уровня, так как она встраивается в процессор. Поэтому при использовании Pentium П и процессоров последующих версий устанавливаются определенные ограничения кэширования памяти. Процессоры с внутренним кэшем первого и второго уровней имеют ограничение, равное соответственно 512 Мбайт и 4 Гбайт, а при использовании Pentium Ш и процессоров последующих версий объем кэшируемой памяти увеличивается до 4 Гбайт. Этот параметр превышает максимальный объем оперативной памяти, которая может поддерживаться тем или другим набором микросхем. Поэтому в подобных системах не следует устанавливать больший объем памяти, чем позволяет контроллер кэш-памяти. Для того чтобы определить ограничения объема кэшируемой памяти, существующие в системе, обратитесь к технической документации набора микросхем системной логики (при использовании систем класса Pentium, процессоров более ранних версий или систем с кэш-памятью, встроенной в системную плату) либо обратите внимание на характеристики процессора (при использовании систем класса Pentium П, процессоров более современных версий или систем с кэш-памятью, встроенной в процессор).

Подсистема памяти

В основе реализации иерархии памяти современных компьютеров лежат два принципа: принцип локальности обращений и соотношение стоимость/производительность. Принцип локальности обращений говорит о том, что большинство программ к счастью не выполняют обращений ко всем своим командам и данным равновероятно, а оказывают предпочтение некоторой части своего адресного пространства.

Иерархия памяти современных компьютеров строится на нескольких уровнях, причем более высокий уровень меньше по объему, быстрее и имеет большую стоимость в пересчете на байт, чем более низкий уровень. Уровни иерархии взаимосвязаны: все данные на одном уровне могут быть также найдены на более низком уровне, и все данные на этом более низком уровне могут быть найдены на следующем нижележащем уровне и так далее, пока мы не достигнем основания иерархии.

Иерархия памяти обычно состоит из многих уровней, но в каждый момент времени мы имеем дело только с двумя близлежащими уровнями. Минимальная единица информации, которая может либо присутствовать, либо отсутствовать в двухуровневой иерархии, называется блоком. Размер блока может быть либо фиксированным, либо переменным. Если этот размер зафиксирован, то объем памяти является кратным размеру блока.

Успешное или неуспешное обращение к более высокому уровню называются соответственно попаданием (hit) или промахом (miss). Попадание - есть обращение к объекту в памяти, который найден на более высоком уровне, в то время как промах означает, что он не найден на этом уровне. Доля попаданий (hit rate) или коэффициент попаданий (hit ratio) есть доля обращений, найденных на более высоком уровне. Иногда она представляется процентами. Доля промахов (miss rate) есть доля обращений, которые не найдены на более высоком уровне.

Поскольку повышение производительности является главной причиной появления иерархии памяти, частота попаданий и промахов является важной характеристикой. Время обращения при попадании (hit time) есть время обращения к более высокому уровню иерархии, которое включает в себя, в частности, и время, необходимое для определения того, является ли обращение попаданием или промахом. Потери на промах (miss penalty) есть время для замещения блока в более высоком уровне на блок из более низкого уровня плюс время для пересылки этого блока в требуемое устройство (обычно в процессор). Потери на промах далее включают в себя две компоненты: время доступа (access time) - время обращения к первому слову блока при промахе, и время пересылки (transfer time) - дополнительное время для пересылки оставшихся слов блока. Время доступа связано с задержкой памяти более низкого уровня, в то время как время пересылки связано с полосой пропускания канала между устройствами памяти двух смежных уровней.

Чтобы описать некоторый уровень иерархии памяти надо ответить на следующие четыре вопроса:

1. Где может размещаться блок на верхнем уровне иерархии? (размещение блока).

2. Как найти блок, когда он находится на верхнем уровне? (идентификация блока).

3. Какой блок должен быть замещен в случае промаха? (замещение блоков).

4. Что происходит во время записи? (стратегия записи).

Организация кэш-памяти

Концепция кэш-памяти возникла раньше чем архитектура IBM/360, и сегодня кэш-память имеется практически в любом классе компьютеров, а в некоторых компьютерах - во множественном числе.

Все термины, которые были определены раньше могут быть использованы и для кэш-памяти, хотя слово "строка" (line) часто употребляется вместо слова "блок" (block).

В таблице 5.3 представлен типичный набор параметров, который используется для описания кэш-памяти.

Таблица 5.3

Типовые значения ключевых параметров для кэш-памяти рабочих станций и серверов

| Размер блока (строки) | 4-128 байт |

| Время попадания (hit time) | 1-4 такта синхронизации (обычно 1 такт) |

| Потери при промахе (miss penalty) (Время доступа - access time) (Время пересылки - transfer time) | 8-32 такта синхронизации (6-10 тактов синхронизации) (2-22 такта синхронизации) |

| Доля промахов (miss rate) | 1%-20% |

| Размер кэш-памяти | 4 Кбайт - 16 Мбайт |

Рассмотрим организацию кэш-памяти более детально, отвечая на четыре вопроса об иерархии памяти. Принципы размещения блоков в кэш-памяти определяют три основных типа их организации:

· Если каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым отображением (direct mapped). Это наиболее простая организация кэш-памяти, при которой для отображение адресов блоков основной памяти на адреса кэш-памяти просто используются младшие разряды адреса блока. Таким образом, все блоки основной памяти, имеющие одинаковые младшие разряды в своем адресе, попадают в один блок кэш-памяти, т.е.

(адрес блока кэш-памяти) =

(адрес блока основной памяти) mod (число блоков в кэш-памяти)

· Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти, то кэш называется полностью ассоциативным (fully associative).

· Если некоторый блок основной памяти может располагаться на ограниченном множестве мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative). Обычно множество представляет собой группу из двух или большего числа блоков в кэше. Если множество состоит из n блоков, то такое размещение называется множественно-ассоциативным с n каналами (n-way set associative). Для размещения блока прежде всего необходимо определить множество. Множество определяется младшими разрядами адреса блока памяти (индексом):

(адрес множества кэш-памяти) =

(адрес блока основной памяти) mod (число множеств в кэш-памяти)

Далее, блок может размещаться на любом месте данного множества.

Диапазон возможных организаций кэш-памяти очень широк: кэш-память с прямым отображением есть просто одноканальная множественно-ассоциативная кэш-память, а полностью ассоциативная кэш-память с m блоками может быть названа m-канальной множественно-ассоциативной. В современных процессорах как правило используется либо кэш-память с прямым отображением, либо двух- (четырех-) канальная множественно-ассоциативная кэш-память.

У каждого блока в кэш-памяти имеется адресный тег, указывающий, какой блок в основной памяти данный блок кэш-памяти представляет. Эти теги обычно одновременно сравниваются с выработанным процессором адресом блока памяти.

Кроме того, необходим способ определения того, что блок кэш-памяти содержит достоверную или пригодную для использования информацию. Наиболее общим способом решения этой проблемы является добавление к тегу так называемого бита достоверности (valid bit).

Адресация множественно-ассоциативной кэш-памяти осуществляется путем деления адреса, поступающего из процессора, на три части: поле смещения используется для выбора байта внутри блока кэш-памяти, поле индекса определяет номер множества, а поле тега используется для сравнения. Если общий размер кэш-памяти зафиксировать, то увеличение степени ассоциативности приводит к увеличению количества блоков в множестве, при этом уменьшается размер индекса и увеличивается размер тега.

При возникновении промаха, контроллер кэш-памяти должен выбрать подлежащий замещению блок. Польза от использования организации с прямым отображением заключается в том, что аппаратные решения здесь наиболее простые. Выбирать просто нечего: на попадание проверяется только один блок и только этот блок может быть замещен. При полностью ассоциативной или множественно-ассоциативной организации кэш-памяти имеются несколько блоков, из которых надо выбрать кандидата в случае промаха. Как правило для замещения блоков применяются две основных стратегии: случайная и LRU.

В первом случае, чтобы иметь равномерное распределение, блоки-кандидаты выбираются случайно. В некоторых системах, чтобы получить воспроизводимое поведение, которое особенно полезно во время отладки аппаратуры, используют псевдослучайный алгоритм замещения.

Во втором случае, чтобы уменьшить вероятность выбрасывания информации, которая скоро может потребоваться, все обращения к блокам фиксируются. Заменяется тот блок, который не использовался дольше всех (LRU - Least-Recently Used).

Достоинство случайного способа заключается в том, что его проще реализовать в аппаратуре. Когда количество блоков для поддержания трассы увеличивается, алгоритм LRU становится все более дорогим и часто только приближенным. В таблице 5.4 приведены различия в долях промахов при использовании алгоритма замещения LRU и случайного алгоритма.

Таблица 5.4

Сравнение долей промахов для алгоритма LRU и случайного алгоритма замещения при нескольких размерах кэша и разных ассоциативностях при размере блока 16 байт

| Ассоциативность: | 2-канальная | 4-канальная 8-канальная |

| Размер кэш-памяти | LRU Random | LRU Random LRU Random |

| 16 KB | 5.18% 5.69% | 4.67% 5.29% 4.39% 4.96% |

| 64 KB | 1.88% 2.01% | 1.54% 1.66% 1.39% 1.53% |

| 256 KB | 1.15% 1.17% | 1.13% 1.13% 1.12% 1.12% |

При обращениях к кэш-памяти на реальных программах преобладают обращения по чтению. Все обращения за командами являются обращениями по чтению и большинство команд не пишут в память. Обычно операции записи составляют менее 10% общего трафика памяти. Желание сделать общий случай более быстрым означает оптимизацию кэш-памяти для выполнения операций чтения, однако при реализации высокопроизводительной обработки данных нельзя пренебрегать и скоростью операций записи. Причем, общий случай является и более простым. Блок из кэш-памяти может быть прочитан в то же самое время, когда читается и сравнивается его тег. Таким образом, чтение блока начинается сразу как только становится доступным адрес блока. Если чтение происходит с попаданием, то блок немедленно направляется в процессор. Если же происходит промах, то от заранее считанного блока нет никакой пользы, правда нет и никакого вреда.

Однако при выполнении операции записи ситуация коренным образом меняется. Именно процессор определяет размер записи (обычно от 1 до 8 байтов) и только эта часть блока может быть изменена. В общем случае это подразумевает выполнение над блоком последовательности операций чтение - модификация - запись: чтение оригинала блока, модификацию его части и запись нового значения блока. Более того, модификация блока не может начинаться до тех пор, пока проверяется тег, чтобы убедиться в том, что обращение является попаданием. Поскольку проверка тегов не может выполняться параллельно с другой работой, то операции записи отнимают больше времени, чем операции чтения.

Очень часто организация кэш-памяти в разных машинах отличается именно стратегией выполнения записи. Когда выполняется запись в кэш-память имеются две базовые возможности:

· сквозная запись (write through, store through) - информация записывается в два места: в блок кэш-памяти и в блок более низкого уровня памяти.

· запись с обратным копированием (write back, copy back, store in) - информация записывается только в блок кэш-памяти. Модифицированный блок кэш-памяти записывается в основную память только когда он замещается. Для сокращения частоты копирования блоков при замещении обычно с каждым блоком кэш-памяти связывается так называемый бит модификации (dirty bit). Этот бит состояния показывает был ли модифицирован блок, находящийся в кэш-памяти. Если он не модифицировался, то обратное копирование отменяется, поскольку более низкий уровень содержит ту же самую информацию, что и кэш-память.

Оба подхода к организации записи имеют свои преимущества и недостатки. При записи с обратным копированием операции записи выполняются со скоростью кэш-памяти, и несколько записей в один и тот же блок требуют только одной записи в память более низкого уровня. Поскольку в этом случае обращения к основной памяти происходят реже, вообще говоря требуется меньшая полоса пропускания памяти, что очень привлекательно для мультипроцессорных систем. При сквозной записи промахи по чтению не влияют на записи в более высокий уровень, и, кроме того, сквозная запись проще для реализации, чем запись с обратным копированием. Сквозная запись имеет также преимущество в том, что основная память имеет наиболее свежую копию данных. Это важно в мультипроцессорных системах, а также для организации ввода/вывода.

Когда процессор ожидает завершения записи при выполнении сквозной записи, то говорят, что он приостанавливается для записи (write stall). Общий прием минимизации остановов по записи связан с использованием буфера записи (write buffer), который позволяет процессору продолжить выполнение команд во время обновления содержимого памяти. Следует отметить, что остановы по записи могут возникать и при наличии буфера записи.

При промахе во время записи имеются две дополнительные возможности:

· разместить запись в кэш-памяти (write allocate) (называется также выборкой при записи (fetch on write)). Блок загружается в кэш-память, вслед за чем выполняются действия аналогичные выполняющимся при выполнении записи с попаданием. Это похоже на промах при чтении.

· не размещать запись в кэш-памяти (называется также записью в окружение (write around)). Блок модифицируется на более низком уровне и не загружается в кэш-память.

Обычно в кэш-памяти, реализующей запись с обратным копированием, используется размещение записи в кэш-памяти (в надежде, что последующая запись в этот блок будет перехвачена), а в кэш-памяти со сквозной записью размещение записи в кэш-памяти часто не используется (поскольку последующая запись в этот блок все равно пойдет в память).

Увеличение производительности кэш-памяти. Формула для среднего времени доступа к памяти в системах с кэш-памятью выглядит следующим образом:

Среднее время доступа = Время обращения при попадании +

+ Доля промахов × Потери при промахе

Эта формула наглядно показывает пути оптимизации работы кэш-памяти: сокращение доли промахов, сокращение потерь при промахе, а также сокращение времени обращения к кэш-памяти при попадании. В таблице 5.5 кратко представлены различные методы, которые используются в настоящее время для увеличения производительности кэш-памяти. Использование тех или иных методов определяется прежде всего целью разработки, при этом конструкторы современных компьютеров заботятся о том, чтобы система оказалась сбалансированной по всем параметрам.

Последнее изменение этой страницы: 2017-07-07

lectmania.ru. Все права принадлежат авторам данных материалов. В случае нарушения авторского права напишите нам сюда...