Категории:

ДомЗдоровьеЗоологияИнформатикаИскусствоИскусствоКомпьютерыКулинарияМаркетингМатематикаМедицинаМенеджментОбразованиеПедагогикаПитомцыПрограммированиеПроизводствоПромышленностьПсихологияРазноеРелигияСоциологияСпортСтатистикаТранспортФизикаФилософияФинансыХимияХоббиЭкологияЭкономикаЭлектроника

Аксиомы и теоремы булевой алгебры

Введение

Разработка любого радиоэлектронного устройства сопровождается физическим или математическим моделированием. Физическое моделирование связано с большими материальными затратами, поскольку требуется изготовление макетов и их трудоемкое исследование. Часто физическое моделирование просто невозможно из-за чрезвычайной сложности устройства, например, при разработке больших и сверхбольших интегральных микросхем. В этом случае прибегают к математическому моделированию с использованием средств и методов вычислительной техники. Например, известный пакет P-CAD содержит блок логического моделирования цифровых устройств, однако для начинающих, в том числе и для студентов, он представляет значительные трудности в освоении. Не меньшие трудности встречаются и при использовании системы DesignLab. Как показал анализ состояния программного обеспечения схемотехнического моделирования, на этапе начального освоения методов автоматизированного проектирования и на этапах проведения поисково-исследовательских работ целесообразно рассмотреть возможность использования следующих программ.

Micro-Cap V — разработка фирмы Spectrum Software (www.spectrum-soft.com), выпускается для платформ IBM, NEC и Macintosh. В версиях для IBM и NEC PC требуется процессор не ниже 80386 с сопроцессором, 15 Мбайт свободного пространства на жестком диске, Windows 3.хх или выше. Имеется библиотека моделей 10 тыс. электрорадиоэлементов ведущих фирм Японии, Европы и США. Программа позволяет:

- создать принципиальную электрическую схему устройства и отредактировать ее;

- провести расчет статического режима по постоянному току;

- рассчитать частотные характеристики и переходные процессы;

- провести оценку уровня внутреннего шума и предельной чувствительности;

- провести многовариантный анализ, включая статистический анализ по методу Монте-Карло;

- наращивать библиотеку компонентов;

- представлять данные в форме, удобной для интерпретации и дальнейшего анализа;

- реализовать другие сервисные функции, типичные для такого класса программ.

DesignLab 8.0 — интегрированный пакет корпорации MicroSim (www.orcad.com), в состав которого входит известная программа моделирования PSpice. Этот пакет позволяет проводить сквозное проектирование радиоэлектронных устройств: от ввода принципиальной схемы, ее моделирования до создания управляющих файлов для программаторов, разработки печатных плат и управляющих программ для сверлильных станков и вывода данных на графопостроитель.

Aplac 7.0 — пакет с типичным набором возможностей, перечисленных выше (www,aplac.hut.fi/aplac). Программа позволяет также моделировать устройства СВЧ диапазона, в частности, она содержит подпрограмму расчета трехмерных электромагнитных полей микрополосковых конструкций и других устройств СВЧ-техники. Программа позволяет вводить и выводить данные с помощью интерфейсных плат стандарта IEEE-488.

System View 1.9 — программа фирмы Elanix (www.elanix.com), содержит типичный набор функций для схемотехнического моделирования, а также богатый математический аппарат для обработки полученных результатов. Программа позволяет моделировать устройства на уровне функциональных схем.

Electronics Workbench (EWB) — разработка фирмы Interactive Image Technologies (www.interactiv.com). Особенностью программы является наличие контрольно-измерительных приборов, по внешнему виду и характеристикам приближенных к их промышленным аналогам. Программа легко осваивается и достаточно удобна в работе. После составления схемы и ее упрощения путем оформления подсхем моделирование начинается щелчком обычного выключателя.

CircuitMaker 6.0 — разработка фирмы MicroCode Engineering (www.microcode.com), содержит обширную библиотеку моделей промышленных изделий электронных компонентов с возможностью оперативного просмотра их основных характеристик (например, для транзистора — это тип корпуса, максимальное напряжение, ток, частота, фирма-изготовитель и др.). Программа позволяет достаточно оперативно подготавливать электрические схемы аналоговых, цифровых или смешанных аналого-цифровых устройств и проводить их моделирование с получением результатов в виде осциллограмм сигналов и графиков частотных характеристик; возможно получение точных отсчетов с помощью вертикальных и горизонтальных визирных линий. Она также позволяет контролировать режим по постоянному току в выбранных точках схемы. Отличительной особенностью программы является наличие анимационных компонентов (запуск ракеты, старт автомобилей), призванных имитировать конечный результат работы схемы, а также то, что она содержит учебное пособие в демонстрационном режиме. Интегрируется с программой разработки печатных плат TraxMaker. Имеются коммерческие и студенческие версии.

Поскольку данное учебное пособие предназначено для студентов младших курсов, еще не получивших углубленные знания в специальных дисциплинах, в качестве основного инструментария для выполнения лабораторных и курсовых работ авторами пособия рекомендуется программа Electro-nics Workbench (EWB) как отличающаяся самым простым и легко осваиваемым пользовательским интерфейсом. Необходимо также отметить, что как учебная программа EWB обладает весьма важным достоинством, которое заключается в развитии творческого начала учащегося: он может не только выполнять задания преподавателя, но и имеет возможность предложить и апробировать свои технические решения, а это уже творчество, которое превращает учебный процесс в увлекательное занятие.

История создания программы Electronics Workbench (EWB) начинается с 1989 г. Ранние версии программы состояли из двух независимых частей. С помощью одной половины программы можно было моделировать аналоговые устройства, с помощью другой — цифровые. Такое "раздвоенное" состояние создавало определенные неудобства, особенно при моделировании смешанных аналого-цифровых устройств. В 1996 г, в версии 4.1 эти части были объединены и через полгода выпущена пятая версия программы. Она дополнена средствами анализа примерно в объеме программы Micro-Cap V, переработана и несколько расширена библиотека компонентов. Средства анализа цепей выполнены в типичном для всей программы ключе — минимум усилий со стороны пользователя. Дальнейшим развитием EWB является программа EWB Layout, предназначенная для разработки печатных плат. Программа EWB обладает преемственностью снизу вверх, т.е. все схемы, созданные в версиях 3.0 и 4.1, могут быть промоделированы в версии 5.0. Следует отметить, что EWB позволяет также моделировать устройства, для которых задание на моделирование подготовлено в текстовом формате SPICE, обеспечивая совместимость с программами Micro-Cap и PSpice.

Согласно данным фирмы Interactive Image Technologies, программа Electronics Workbench в настоящее время насчитывает около 85 тыс. зарегистрированных пользователей. Судя по рекламным листкам и каталогам, распространяемых компанией "Софт Лайн" (дистрибьютором Electronics Workbench в странах СНГ), основными пользователями программы являются средние и высшие учебные заведения. Об этом говорит и тот факт, что наряду с самой программой в прайс-листе фирмы содержится обширный список учебных пособий, созданных на базе EWB. Пока в списке нет пособия по использованию пакета EWB Layout, поскольку это достаточно новая разработка. В процессе знакомства с программой и примерами ее многочисленных применений можно убедиться, что весьма удобный пользовательский интерфейс EWB действительно являются серьезной предпосылкой для использования ее в учебных целях в качестве лабораторного практикума по таким предметам, как физика (электричество), основы электротехники и электроники, основы вычислительной техники и автоматики.

Программа EWB 4.1 рассчитана для работы в среде Windows 3.хх или 05/98 и занимает около 5 Мбайт дисковой памяти, EWB 5.0 — в среде Windows 95/98/ХР и NT, требуемый объем дисковой памяти — около 16 Мбайт. Для размещения временных файлов требуется дополнительно 10 — 20 Мбайт свободного пространства.

Булева алгебра

Логические функции.

| X: 0 1 0 1 | Условное обозначение | Название | |

| Y: 0 0 1 1 | |||

| f0 | 0 0 0 0 | “0” | |

| f1 | 0 0 0 1 | “Ù”(×) | Конъюнкция (И) |

| f2 | 0 0 1 0 |  (YDX) (YDX)

| Запрет Х |

| f3 | 0 0 1 1 | Y | |

| f4 | 0 1 0 0 |  (XDY) (XDY)

| Запрет Y |

| f5 | 0 1 0 1 | X | |

| f6 | 0 1 1 0 | XÅY | Исключающее ИЛИ |

| f7 | 0 1 1 1 | “Ú”(+) | Дизъюнкция (ИЛИ) |

| f8 | 1 0 0 0 | X¯Y (  ) )

| Стрелка Пирса (ИЛИ-НЕ) |

| f9 | 1 0 0 1 |  (~) (~)

| Равнозначность |

| F10 | 1 0 1 0 |

| |

| F11 | 1 0 1 1 | X®Y (  ) )

| Импликация от X к Y |

| F12 | 1 1 0 0 |

| |

| F13 | 1 1 0 1 | Y®X (  ) )

| Импликация от Y к X |

| F14 | 1 1 1 0 | X|Y (  ) )

| Штрих Шеффера (И-НЕ) |

| F15 | 1 1 1 1 | “1” |

Составление булевых выражений по таблице

истинности

Правило единиц. Выбирают строки в которых функция принимает значение “1”. Для этих строк составляют конъюнкцию аргументов (минтерму) и полученные конъюнкции объединяются знаком дизъюнкции. Такое выражение называется булевым каноническим произведением или стандартным произведением сумм или конъюнктивной нормальной формой.

Правило нулей. Выбирают строки в которых функция равна “0”. Для этих строк составляют дизъюнкции аргументов (макстермов). Полученные дизъюнкции объединяют знаком конъюнкции.

Изучение дешифраторов

Краткие сведения из теории

Дешифратор - логическая комбинационная схема, которая имеет n информационных входов и  выходов. Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов.

выходов. Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов.

Рис.1.1

Рис.1.1

| Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2п выходов. Обычно n равно 2,3 или 4. На рис. 1.1 изображен дешифратор с n = 3, активным уровнем является уровень логического нуля (в данной лабораторной работе для удобства вместо схемы дешифратора используется схема демультиплексора, это возможно благодаря сходству алгоритмов работы). |

На входы С, В, А можно подать следующие комбинации логических уровней: 000, 001, 010, ..., 111, всего 8 комбинаций. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал, на остальных - высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует числу N, определяемому состоянием входов С, В, А следующим образом: N = С∙22 + В∙21 + А∙20.

Например, если на входы подана комбинация логических уровней 011, то из восьми выходов микросхемы (YO, Y1,...,Y7) на выходе с номером N=3 установится нулевой уровень сигнала (Y3=0), a все остальные выходы будут иметь уровень логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

Уровень сигнала на выходе Y3 описывается выражением

.

.

В таком же виде можно записать выражения для каждого выхода дешифратора:

,

,  ,

,

,

,  ,

,

,

,  ,

,

,

,  .

.

Помимо информационных входов А, В, С дешифраторы обычно имеют дополнительные входы управления G. Сигналы на этих входах, например, разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов.

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом - уровень логического нуля. На рис. 1.1 представлен дешифратор с одним инверсным входом управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора 74138 с одним прямым входом управления G1 и двумя инверсными G2A и G2B (рис. 1.2) функции выхода  и разрешения G имеют вид:

и разрешения G имеют вид:

.

.

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

Рис. 1.2

Рис. 1.2

| Дешифратор может быть использован и как демультиплексор - логический коммутатор, подключающий входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов С, В и А задает номер выхода, на который передается сигнал со входа разрешения. |

Эксперимент 1. Исследование принципа работы дешифратора 3x8 в основном режиме

Соберите схему, изображенную на рис 1.3. Включите схему. Подайте на вход G уровень логической единицы. Для этого клавишей G ключ G установить в верхнее положение. Определите и запишите уровни сигналов на выходах YO...Y7 в таблицу истинности при G=1 (табл. 1.1).

Подайте на вход G уровень логического нуля (ключ G установите в нижнее положение). Убедитесь, что дешифратор перешел в рабочий режим и на одном из выходов установился уровень логического нуля. Подавая все возможные комбинации уровней логических сигналов на входы А, В, С с помощью одноименных ключей и определяя с помощью логических пробников уровни логических сигналов на выходе схемы, заполните таблицу истинности дешифратора при G=0.

Таблица 1.1

| G | A | B | C | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

Эксперимент 2. Исследование дешифратора 3´8 с логической схемой на выходе

Соберите схему, изображенную на рис. 1.6. Включите схему. Установите генератор слов в пошаговый режим. Последовательно подавая слова от генератора на вход схемы и наблюдая уровень логического сигнала на выходе схемы с помощью логического пробника, составьте таблицу истинности функции F, реализуемой схемой на выходе. По таблице запишите аналитическое выражение функции.

Эксперимент 3. Исследование микросхемы 74138

а) Соберите схему (рис. 1.7). Установите генератор слов в пошаговый режим. Включите схему. С помощью соответствующих ключей установите состояние управляющих входов Gl=0, G2A=G2B=1. Подавая на входы А, В, С слова от генератора слов и наблюдая состояние выходов с помощью логических пробников, заполните таблицу функционирования дешифратора 74138.

б) Повторите операции пункта а) при G1=G2A=1, G2B=0. Заполните таблицу функционирования дешифратора 74138.

в) Повторите операции пункта а) при Gl=l, G2A=G2B=0. Заполните таблицу функционирования дешифратора 74138.

г) Повторите операции пункта а) при Gl=l, G2A=G2B=1. Заполните таблицу функционирования дешифратора 74138.

ЗАДАНИЕ К КОНТРОЛЬНОЙ РАБОТЕ № 1

1. Разработайте, соберите и испытайте схемы на основе базового дешифратора и элементов 2И-НЕ или 2И, реализующие заданную функцию F. На входе разрешения установить активный уровень. Варианты задач приведены ниже.

Для выполнения задания возьмите двойную инверсию от функции и раскройте внутреннюю по теореме де Моргана.

| Вариант 1 |

|

| Вариант 2 |

|

| Вариант 3 |

|

| Вариант 4 |

|

| Вариант 5 |

|

| Вариант 6 |

|

| Вариант 7 |

|

| Вариант 8 |

|

| Вариант 9 |

|

| Вариант 10 |

|

| Вариант 11 |

|

| Вариант 12 |

|

| Вариант 13 |

|

| Вариант 14 |

|

| Вариант 15 |

|

| Вариант 16 |

|

| Вариант 17 |

|

| Вариант 18 |

|

| Вариант 19 |

|

| Вариант 20 |

|

Краткие сведения из теории

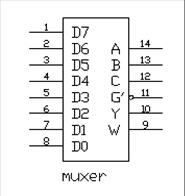

Мультиплексор - комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на входах управления. Кроме информационных и управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход

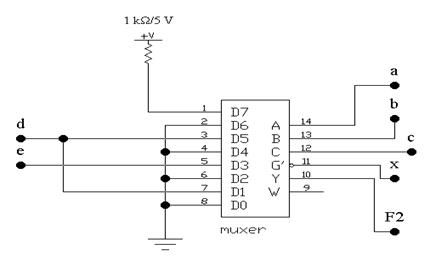

Рис. 2.1 Рис. 2.1

| разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и управляющих сигналов.Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На рис. 2.1 представлен мультиплексор 8x1 с инверсным входом разрешения G, прямым Y и инверсным W-выходами (  ). ).

|

Уравнение работы мультиплексора

Функционирование мультиплексора, представленного на рис. 2.1, описывается характеристическим уравнением, связывающим сигнал на выходе (Y) с разрешающим (G), входными информационными (D0 … D7) и управляющими (А, В, С) сигналами:

Как видно из уравнения, на мультиплексоре можно реализовать логические функции, для чего нужно определить, какие сигналы и логические константы следует подавать на входы мультиплексора.

Реализация заданной функции с помощью мультиплексора

Логическая функция n переменных определена для  комбинаций значений переменных. Это позволяет реализовать функцию n переменных на мультиплексоре, имеющем n управляющих и

комбинаций значений переменных. Это позволяет реализовать функцию n переменных на мультиплексоре, имеющем n управляющих и  информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции.

информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции.

Например, требуется реализовать функцию

Эта функция определена только для 8 комбинаций значений переменных, поэтому для её реализации можно использовать мультиплексор 8x1 с тремя управляющими входами. Составим таблицу истинности функции (табл.2.1).

| Таблица 2.1 | ||||

| DN | c | b | a | F1 |

| D0 | ||||

| D1 | ||||

| D2 | ||||

| D3 | ||||

| D4 | ||||

| D5 | ||||

| D6 | ||||

| D7 |

Из таблицы видно, что для реализации функции на мультиплексоре необходимо подать на информационный вход мультиплексора с номером N сигнал, значение которого равно соответствующему значению функции F1, т.е. на входы D0, D1, D5, D7 следует подать уровень логической единицы, а на остальные - уровень логического нуля. Таким образом, при подаче комбинации логических уровней на управляющие входы мультиплексора к его выходу подключится вход, значение сигнала на котором равно соответствующему значению функции. Схемная реализация приведена на рис. 2.2.

Рис. 2.2

При реализации логических функций на информационные входы можно подавать не только константы, но и изменяющиеся входные сигналы. Так, например, рассмотрим другой способ реализации функции F1, рассмотренной выше. Для этого минимизируем выражение функции  .

.

Составим таблицу истинности функции в зависимости от значений переменных а и b (табл. 2.2).

| Таблица 2.2 | |||

| N | b | A | F1 |

| |||

| с |

Заданную такой таблицей функцию реализуют, как и в предыдущем случае, подав на вход с номером N сигнал, значение которого соответствует значению функции F1. В данном случае сигналы с и  , соответствующие переменной с, подаются на информационные входы, как указано в таблице истинности. При этом сокращается число управляющих входов.

, соответствующие переменной с, подаются на информационные входы, как указано в таблице истинности. При этом сокращается число управляющих входов.

Схемная реализация такого способа задания функции представлена на рис. 2.3. Так как используются только два адресных входа, управляющий вход С можно заземлить. При этом состояние информационных входов D4...D7 безразлично. Уровень сигнала на выходе схемы определяется комбинацией уровней сигналов в точках А, В, С, соответствующих переменным а, b, с. Схема рис. 2.3 по существу представляет собой мультиплексор 4x1 с двумя управляющими и четырьмя информационными входами.

Рис. 2.3

Если функцию можно представить в виде произведения одночлена на многочлен, то её также можно реализовать при помощи мультиплексора. Как следует из уравнения мультиплексора, сигнал, соответствующий одночлену, нужно подать на вход разрешения. Например, требуется реализовать функцию F2, описываемую следующим выражением:

.

.

При реализации данной функции на мультиплексоре сигнал, соответствующий переменной x, следует подать на его разрешающий вход. Рассмотрим, какие сигналы необходимо подать на управляющие входы мультиплексора. Выражение в скобках можно рассматривать как некоторую функцию f пяти переменных: а, b, с, d, е, из которых наиболее часто используются переменные a, b и с. Поэтому сигналы, соответствующие этим переменным, нужно подать на управляющие входы мультиплексора.

Определим, какие сигналы следует подать на информационные входы, чтобы реализовать функциюf. Для этого составим таблицу истинности функции в зависимости от значений переменных a, b и с(табл. 2.3).

| Таблица 2.3 | ||||

| N | C | b | a | f |

| d | ||||

| e | ||||

| d | ||||

Из таблицы видно, что на входы с номерами N = 0, 2, 4, 6 нужно подать уровень логического нуля. Сигнал, соответствующий переменной d, нужно подать на входы с номерами N = 1, 5, сигнал, соответствующий переменной е, - на вход с номером 3. Схемная реализация представлена на рис. 2.4.

Рис. 2.4

ЗАДАНИЕ К КОНТРОЛЬНОЙ РАБОТЕ № 2

1. Разработать, собрать и проверить работу схемы на основе мультиплексора 8×1, реализующую заданную логическую функцию Y. Варианты задач указаны ниже.

| Вариант 1 |

|

| Вариант 2 |

|

| Вариант 3 |

|

| Вариант 4 |

|

| Вариант 5 |

|

| Вариант 6 |

|

| Вариант 7 |

|

| Вариант 8 |

|

| Вариант 9 |

|

| Вариант 10 |

|

| Вариант 11 |

|

| Вариант 12 |

|

| Вариант 13 |

|

| Вариант 14 |

|

| Вариант 15 |

|

| Вариант 16 |

|

| Вариант 17 |

|

| Вариант 18 |

|

| Вариант 19 |

|

| Вариант 20 |

|

Краткие сведения из теории

У рассмотренных выше комбинационных схем состояние выхода Y в любой момент времени определяется только текущим состоянием входа X:

Y = F(X).

В отличие от них, состояние выхода последовательностной схемы (цифрового автомата) зависит еще и от внутреннего состояния схемы Q:

Y = F(X,Q).

Это свойство обеспечивается наличием в схемах обратных связей.

Основой последовательностных схем являются триггеры. Триггер имеет два устойчивых состояния:  и

и  , поэтому его иногда называют бистабильной схемой. В каком из этих состояний окажется триггер, зависит от сигналов на входах триггера и от его предыдущего состояния, т. е. он имеет память. Можно сказать, что триггер является элементарной ячейкой памяти.

, поэтому его иногда называют бистабильной схемой. В каком из этих состояний окажется триггер, зависит от сигналов на входах триггера и от его предыдущего состояния, т. е. он имеет память. Можно сказать, что триггер является элементарной ячейкой памяти.

Тип триггера определяется алгоритмом его работы. В зависимости от алгоритма работы, триггер может иметь установочные, информационные и управляющие входы. Установочные входы устанавливают состояние триггера независимо от состояния других входов. Входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS, JK, D и Т-типов.

Триггер типа RS

| RS-триггер - простейший автомат с памятью, который может находиться в двух состояниях. Триггер имеет два установочных входа: установки S (set - установка) и сброса R (reset - сброс), на которые подаются входные сигналы от внешних источников. |

При подаче на вход установки активного логического уровня триггер устанавливается в 1 (  ,

,  ), при подаче активного уровня на вход сброса триггер устанавливается в 0 (

), при подаче активного уровня на вход сброса триггер устанавливается в 0 (  ,

,  ). Если подать на оба входа установки (возбуждения) пассивный уровень, то триггер будет сохранять предыдущее состояние выходов:

). Если подать на оба входа установки (возбуждения) пассивный уровень, то триггер будет сохранять предыдущее состояние выходов:  (

(  ) либо

) либо  (

(  ). Каждое состояние устойчиво и поддерживается за счет действия обратных связей.

). Каждое состояние устойчиво и поддерживается за счет действия обратных связей.

Для триггеров этого типа является недопустимой одновременная подача активного уровня на оба входа установки, так как триггер по определению не может одновременно быть установлен в 0 и 1. На практике подача активного уровня на установочные входы приводит к тому, что это состояние не может быть сохранено и невозможно определить, в каком состоянии будет находиться триггер при последующей подаче на установочные входы сигналов пассивного уровня.

На рис. 3.1 и 3.2 показаны два вида RS-триггеров, выполненных на элементах ИЛИ-НЕ и И-НЕ.

Для схемы на рис. 3.1 активным уровнем является уровень логической единицы, для схемы на рис. 3.2 - уровень логического нуля. Схема на рис. 3.2 получила название RS-триггера с инверсными входами - RS-триггер.

Рис. 3.1

Рис. 3.1

|  Рис. 3.2

Рис. 3.2

|

RS-триггер является основным узлом для построения последовательностных схем. Название схем такого типа «последовательностные» означает, что состояние выхода зависит от того, в какой последовательности на входы подаются входные наборы и, каково было предшествующее внутреннее состояние. Так, если в RS-триггере (рис. 3.1) вначале установить комбинацию  ,

,  (сокращенная запись - 01), а потом перейти к

(сокращенная запись - 01), а потом перейти к  ,

,  (00), то состояние выхода

(00), то состояние выхода  . Если вначале установить комбинацию 10, а потом перейти к 00, то состояние выхода будет другим -

. Если вначале установить комбинацию 10, а потом перейти к 00, то состояние выхода будет другим -  , несмотря на одинаковые комбинации сигналов на входах. Таким образом, при одном и том же входном наборе 00 выход триггера может находиться в разных состояниях.

, несмотря на одинаковые комбинации сигналов на входах. Таким образом, при одном и том же входном наборе 00 выход триггера может находиться в разных состояниях.

Условия переходов триггеров из одного состояния в другое (алгоритм работы) можно описать табличным, аналитическим или графическим способами. Описание работы RS-триггера (рис. 3.1) представлено в таблице истинности 3.1, RS-триггера с инверсными входами (рис. 3.2) - в табл. 3.2.

Таблица 3.1

| R | S |

| Режим работы |

| Хранение | ||

| Установка «1» | |||

| Установка «0» | |||

| - | Запрещенное состояние |

Таблица 3.2

| R | S |

| Режим работы |

| Хранение | ||

| Установка «1» | |||

| Установка «0» | |||

| - | Запрещенное состояние |

В таблицах использованы следующие обозначения:

Qt - предшествующее состояние выхода;

Qt+1 - новое состояние, устанавливающееся после перехода;

“ – ”- неопределенное состояние.

Аналитическое описание (характеристическое уравнение) можно получить из табл. 3.1 по правилам алгебры логики:

Синхронный RS-триггер

Условное обозначение синхронного RS-триггера приведено на рис. 3.3. Триггер имеет дополнительно два логических элемента И-НЕ и синхронизирующий вход С, как показано на рис.3.4.

Рис. 3.3

Рис. 3.3

|  Рис. 3.4

Рис. 3.4

|

Таблица истинности синхронного RS-триггера приведена в табл. 3.3.

Таблица 3.3

| С | R | S |

| Режим работы |

| х | х |

| Хранение | |

| |

||||

|

Последнее изменение этой страницы: 2017-07-07 lectmania.ru. Все права принадлежат авторам данных материалов. В случае нарушения авторского права напишите нам сюда... |